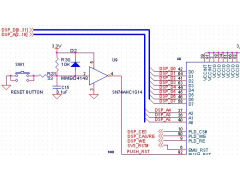

Cadence 高速PCB的时序分析(1)

2013-01-09

宋宝华

20

1.引言 时序分析,也许是SI 分析中难度最大的一部分。我怀着满腔的期许给Cadence 的资深工程师发了一封e-mail,希望能够得到一份时序分析的案例,但是希望化作了泡影。资深工程师告诉我,他们还没有能够编写一个具体的案例。于是,我不得不将我的期许转化为自己研究并编写一个具体的案例,与广大PCB 工程师共享,令大彼天下P ..

[查看全文]

Cadence 高速PCB的时序分析(2)

2012-12-27

13

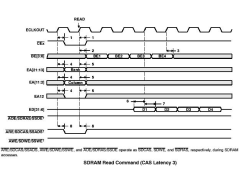

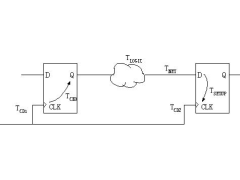

列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍什么是定时问题,怎样保证接收端的建立和保持时间。 信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以 ..

[查看全文]

高速PCB设计中的时序分析及仿真策略

2012-12-25

秦洪密 李军

26

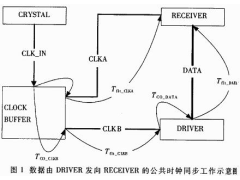

写在前面: 由于不是每个项目要求时间精度达到ns级,因此做同步电路的时候可以忽略很多设计因素.但是导致同步电路出现故障的原因,却大都是没有考虑同步电路的典型 特性和规则.作为新手,如果想从初步设计开始向进阶迈进,推荐阅读以下的文字.文章也许不一定100%正确,但是值得细细推敲和消化,有耐心的应该能有收获. 硕士博士可以 ..

[查看全文]

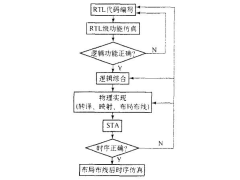

静态时序分析(Static Timing Analysis)基础与应用(上)

2012-10-27

陳麒旭

30

前言 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

27

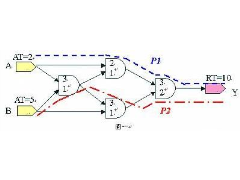

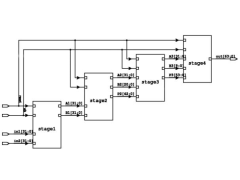

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

约束、时序分析的概念

2012-06-02

9

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?为了解决大家的疑难 ..

[查看全文]

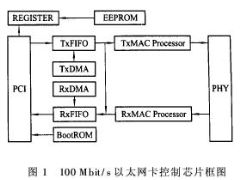

100Mbit/s以太网卡芯片设计与静态时序分析

2012-06-02

黎声华 莫迟

15

在专用集成电路的设计过程中,验证是最关键的一环,它贯穿了整个EDA设计流程.而在深亚微米芯片设计中,只有用实际的布图拓扑信息约束逻辑设计,才能得到准确的时序.在这种情形下静态时序分析应运而生,它可以利用从实际的布图拓扑信息得到的准确时序,根据设计规范的要求对设计进行检查而不需要测试向量,同时还能对设计本身作全面 ..

[查看全文]

静态时序分析(Static Timing Analysis)基础及应用(下)

2012-06-02

陈麒旭

22

前言 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成為今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者指定的时序下正常工作,对确保IC品质之课题,提供一个不错 ..

[查看全文]

推荐文章

最新文章

热门文章