高速数字电路板设计技术探索

2012-12-27

宇量

37

随着数字电子产品小型化、高速化的市场需求,数字电路板的设计日益受到重视。由于高速数字电路大多是小型CMOS组件所构成,因此本文以FR-4电路板为前提,深入探讨有关高速数字电路板的设计技巧。 设计高速数字电路板的20项要诀 使用低诱电率与低诱电正接的电路板 高诱电率的电路板容易导通电磁界,因此极易受到噪讯干扰,一般 ..

[查看全文]

容易被忽略的数字电路设计要点提要

2012-12-13

12

最近对fpga的讨论越来越偏重于嵌入式系统设计,在altera论坛上开始看到对nios感兴趣的人也越来越多。然而,过分倾向于sopc与dsp builder的应用毕竟不是很好的学习方法。要知道,这些都是一种实现工具,而实现的构思则源于逻辑算法的创造与模仿。在这论点上,硬件描述语言为我们提供一个很好的管道,来表达我们理想的数字系统 ..

[查看全文]

数字电路中去耦电容的作用

2012-11-27

12

数字电路输出信号电平转换过程中会产生很大的冲击电流,在供电线和电源内阻上产生较大的压降,使供电电压产生跳变,产生阻抗噪声(亦称开关噪声),形成干扰源。 一、冲击电流的产生 (1)输出级控制正负逻辑输出的管子短时间同时导通,产生瞬态尖峰电流 (2)受负载电容影响,输出逻辑由“0”转换至“1”时, ..

[查看全文]

流水线技术在高速数字电路设计中的应用

2012-07-18

肖良军

15

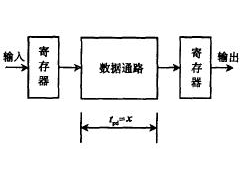

摘要:流水线技术是设计高速数字电路的一种最佳选择之一,对其实现原理作了较形象的阐述。针对加法器在DSP中的重要作用,对流水线加法器中流水线技术的应用作了较深入的说明。同时,对流水线技术中引入寄存器事项也作了较全面的阐述。 1前言 数字信号处理技术(DSP)在许多领域都得到广泛的应用,在数字电路设计时,设计者都希 ..

[查看全文]

数字电路设计盲点实例与对策

2012-06-02

宇量

36

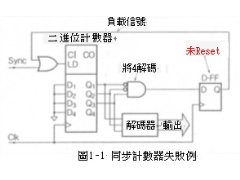

介绍有关数字电路设计盲点的内容,将分别针对Tinning、数据传输、消耗电流、HDL编写等项目,辅以实例进行现象、原因分析以及对策探讨。首先要介绍的是二进制计数器(Binary Counter)的设计。有关Tinning的设计盲点【二进制计数器】二进制计数器经常被用来作外部输入脉冲的同步化,此外计数器的输出可负载(Load)到计数器本身 ..

[查看全文]

推荐文章

最新文章

热门文章