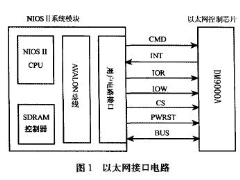

32位软核处理器NIOS II的以太网接口设计与实现

2013-01-22

陈小毛 陈尚松

20

摘要:本文阐述了32位软核处理器NIOS II以太网接口的实现方法,结合SOPC可以灵活配置的特点,定制了硬件系统,给出了软件设计的主要流程及部分实现要点。在FPGA上构建SOPC系统,并在NIOS II上移植了操作系统uClinux,编写了软件驱动程序,通过PC向片上可编程系统发数据包,可以从以太网接口获得所有数据包的返回信息。实 ..

[查看全文]

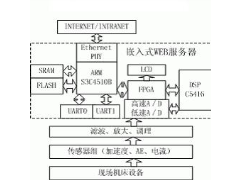

基于ARM和Ethernet的现场实时信号采集分析系统

2012-11-29

杨健 张慧慧

18

摘要: 本文提出了一种基于ARM 和Ethernet现场实时动态信号采集分析系统的软硬件系统实现方案。该方案通过采用ARM+DSP主从结构、嵌入式LINUX系统及合理任务分配策略保证了系统的实时性要求,并将网络数据传输率需求控制在可行范围内。讨论了Ethernet 应用于工业测试诊断系统的相关关键技术问题。 随着计算机技术、网络技术 ..

[查看全文]

CS8900嵌入式以太网pcb设计中的几点注意事项

2012-06-02

13

(本文译自CS8900A PCB手册) 1.数字信号和模拟信号不能混合布线; 2.信号线不能走在cs8900a下面; 3.芯片 3对模拟电源、地对,4对数字电源、地对间都加0.1uF电容,连线尽可能短;连线一端接电容,另一端接网络; 4.两面铺铜,元件层的铺铜连到地网络上,焊接层的铺铜连到电源层; 5.传输线和接收线的终端匹配电阻和电 ..

[查看全文]

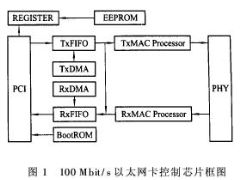

100Mbit/s以太网卡芯片设计与静态时序分析

2012-06-02

黎声华 莫迟

18

在专用集成电路的设计过程中,验证是最关键的一环,它贯穿了整个EDA设计流程.而在深亚微米芯片设计中,只有用实际的布图拓扑信息约束逻辑设计,才能得到准确的时序.在这种情形下静态时序分析应运而生,它可以利用从实际的布图拓扑信息得到的准确时序,根据设计规范的要求对设计进行检查而不需要测试向量,同时还能对设计本身作全面 ..

[查看全文]

推荐文章

最新文章

热门文章