高速PCB设计中的串扰分析与控制

2012-12-09

16

物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的方法,以及电气规则驱动的高速PCB布线技术实现信号串扰控制的设计策略。当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变沿也就越来越快,从而导致高速数字电路系 ..

[查看全文]

使用Allegro SI分析串扰

2012-12-05

76

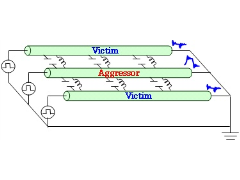

1 概要 高速电路板在进行信号完整性分析的时候,和反射一起的串扰噪声的影响也必须考虑。 本文将介绍串扰噪声的理论基础及如何使用Allegro PCB SI对串扰进行分析: 2 所谓串扰噪声 ※ Aggressor・・・入侵网络 ※ Victim・・・受害网络 众所周知,信号传输线路周围有电磁场发生。当 ..

[查看全文]

高速PCB板设计中的串扰问题和抑制方法

2012-10-26

曾铮

13

在当今飞速发展的电子设计领域,高速化和小型化已经成为设计的必然趋势。与此同时,信号频率的提高、电路板的尺寸变小、布线密度加大、板层数增多而导致的层间厚度减小等因素,则会引起各种信号完整性问题。因此,在进行高速板级设计的时候就必须考虑到信号完整性问题,掌握信号完整性理论,进而指导和验证高速PCB的设计。在 ..

[查看全文]

高速PCB线路串扰初探

2012-08-03

刘汉瑞

61

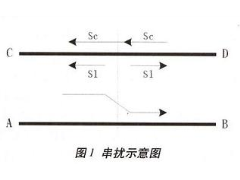

1、引言 串扰可以定义为来自邻近信号对某个信号通路的干扰。其耦合通路是以互容和互感为特征的。在高速PCB线路中串扰会改变系统总线的传输性能,串扰会将噪声感应耦合到其他的传输线上,会降低信号的完整性,导致噪声容限变小,过大的串扰会引电路的误触发,导致系统无法正常工作。随着信号频率变高,信号上升、下降时间减小 ..

[查看全文]

高速PCB串扰分析及其最小化

2012-08-03

乔洪

58

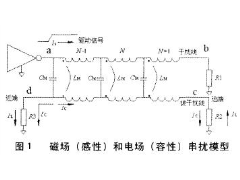

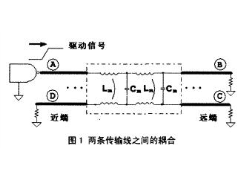

1.引言 随着电子产品功能的日益复杂和性能的提高,印刷电路板的密度和其相关器件的频率都不断攀升,保持并提高系统的速度与性能成为设计者面前的一个重要课题。信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的 ..

[查看全文]

高速串行通信模块中的串扰恶化

2012-07-18

11

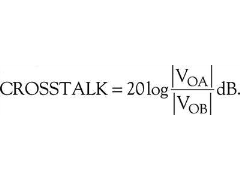

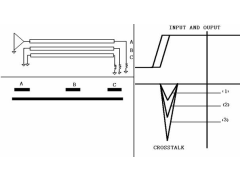

电磁串扰有许多危害,其中一种危害便是降低接收机灵敏度。随着人们要求以增加数据速率来获得更高的吞吐量,以减小模块尺寸来增加端口密度以及通过降低电源线路电压来减少功耗和电路中的串扰变得越来越具挑战性。 两个信道之间的串扰定义为:没有输入信号时信道A的输出除以由输入信号激励的信道B输出所得到的比值。以分贝表示 ..

[查看全文]

推荐文章

最新文章

热门文章