嵌入式系统BootLoader技术内幕

2012-06-11

詹荣开

10

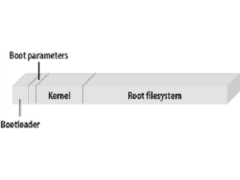

本文详细地介绍了基于嵌入式系统中的 OS 启动加载程序 ―― Boot Loader 的概念、软件设计的主要任务以及结构框架等内容。 在专用的嵌入式板子运行 GNU/Linux 系统已经变得越来越流行。一个嵌入式 Linux 系统从软件的角度看通常可以分为四个层次: 1. 引导加载程序。 包括固化在固件(firmware)中的 boot 代码(可选),和 Boot L ..

[查看全文]

Cadence 仿真流程

2012-06-02

Poqi055

61

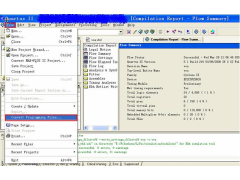

第一章 在Allegro 中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 使用SpecctreQuest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面 ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

39

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

S3C2410 bootloader(vivi)阅读笔记

2012-06-02

10

建议读一读《嵌入式系统Boot Loader技术内幕》(詹荣开著)。什么是Bootloader就不再这里废话了,看看上面的文章就明了了。 Bootloader有很多种,如本文将要阅读的vivi,除此之外还有uboot,redboot,lilo等等。Vivi 是韩国mizi公司专门为三星s3c2410芯片设计的Bootloader。 先来看看vivi的源码树: vivi-+-arch-+-s3c2410 |-D ..

[查看全文]

S3C2410 bootloader全程详解

2012-06-02

13

网上关于Linux的bootloader文章不少了,但是大都是vivi,blob等比较庞大的程序,读起来不太方便,编译出的文件也比较大,而且更多的是面向开发用的引导代码,做成产品时还要裁减,这一定程度影响了开发速度,对初学者学习开销也比较大,在此分析一种简单的bootloader,是在三星公司提供的S3C2410 bootloader上稍微修改后的结果,编译 ..

[查看全文]

使用Flash Loader(JTAG模式)下载EPCS器件

2012-06-02

8

一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。一般使用AS模式下载EPCS系列器件。但有时候可能遇到AS模式不能成功下载的案例,原理图以及PCB板都是按照推荐电路设计,这时候我们可以通过Flash Loader检验EPCS器件是否良好。即通过JTAG方式下载EPCS系列器件。如果这种方 ..

[查看全文]

S3C44B0X上的一款Boot Loader解析

2012-06-02

李娜 许童羽 李征明

12

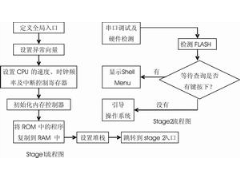

摘要: 本文对Boot Loader的功能、操作模式等作了简单的介绍,重点对基于S3C44B0X内核的UP-NetARM3000上移植uCOS所设计的Boot Loader代码进行了深入的分析和研究,详细的介绍了这款Boot Loader的运行流程和工作机理,为成功装载嵌入式操作系统建立良好的软硬件环境。 一个完整的嵌入式系统包括嵌入式微处理器和外围支 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排...

2012-06-02

41

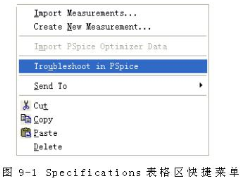

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

如何将OrCAD中的元件的Value传递到PADS 中

2012-06-02

Joison

43

鉴于很多朋友反应,无法将OrCAD 中元件的Value导入到 PADS 中,所以下面我将做一下简单的介绍 (我使用的 OrCAD 10.5 版本,PADS是2005) 为每个元件指定PCB 封装,更详细说明 请参考 用Orcad做原理图,用PADS layout 特别要注意的是;添加 ,{Value} 注意 这里的逗号一定要是英文输入法下的逗号,Value这个字段要用大括号 ..

[查看全文]

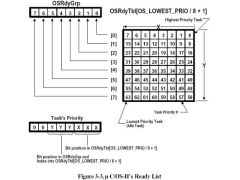

uCOS II就绪表(Ready List)分析

2012-06-02

19

3.0 就绪表(Ready List) 每个任务被赋予不同的优先级等级,从0级到最低优先级OS_LOWEST_PR1O,包括0和OS_LOWEST_PR1O在内(见文件OS_CFG.H)。当uCOS II初始化的时候,最低优先级OS_LOWEST_PR1O总是被赋给空闲任务idle task。注意,最多任务数目OS_MAX_TASKS和最低优先级数是没有关系的。用户应用程序可以 ..

[查看全文]

Cadence的 EDA验证工具在 SOC设计中的应用

2012-06-02

叶 辉

11

摘要: 本文介绍了Cadence公司的NC-Verilog/Verilog-XL Simulator以及Signalscan在SOC设计中的应用。 关键词: SOC,协同验证(co-verification) 在ASIC 和 SOC 设计中,验证是极为重要的一环,Cadence公司的NC-Verilog仿真器(以及较早产品 Verilog-XL)是用来仿真用 Verilog 语言写的数字逻辑电路。该仿真器在 ASIC和SO ..

[查看全文]

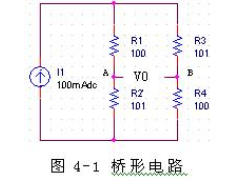

从实例中学习OrCAD-PSpice 10.3-AA(第4章灵敏度分析工具)

2012-06-02

18

想要调用PSpice–AA进行电路优化设计,一般是先进行灵敏度(Sensitivity)分析:以便确定电路中对电路特性影响最大的关键元件参数进行优化。OrCAD9.2以前版本的灵敏度分析,由于有大量数据输出问题没有解决,故只局限于作直流灵敏度分析,置于直流工作点分析内。 直流灵敏度分析:虽然电路特性完全取决于电路中的元器 ..

[查看全文]

推荐文章

最新文章

热门文章