高速PCB设计指南(六)

2012-12-29

22

第一篇混合信号电路板的设计准则模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的 “真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟效应,例如当从低电平向高电平(状态) ..

[查看全文]

Cadence 高速PCB的时序分析(2)

2012-12-27

13

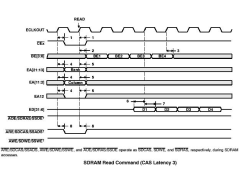

列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍什么是定时问题,怎样保证接收端的建立和保持时间。 信号经过传输线到达接收端之后,必须满足建立时间和保持时间这两个时序参数,它们由接收器本身的特性决定,可以 ..

[查看全文]

Protel中有关PCB工艺的条目简介

2012-12-26

王韬

12

不少初学者感到Protel软件本身简单易学,容易上手,但较难理解的反倒是软件以外的一些概念和术语。为推广这一强有力的EDA工具,国内出版了该软件的使用手册等等,但遗憾的是,这些读物往往都是针对软件使用方法本身而编写的,对读者颇感困惑的PCB I艺中有关概念鲜有解释。笔者拟就软件涉及到的与PCB工艺的条目。撷摘若干, ..

[查看全文]

DXF文件转为POWERPCB文件

2012-12-26

22

DXF 是含 Vector, Text 的 Multi-Layer 图档 PADS/PowerPCB 会读取其中的 2D-Line(Vector 的一种), Text 这两个 Item PADS/PowerPCB 的 Layer Name 命名规则 PADS Layer Name 例子 BRD00: 板框 LIN01: 2D-Line, PADS 第 1 层 TXT01: Text, PADS 第 1 层 ... Layer Name 要 PADS 可以识别的才会载入 且不会载入 LIN01 ..

[查看全文]

高速PCB设计中的时序分析及仿真策略

2012-12-25

秦洪密 李军

26

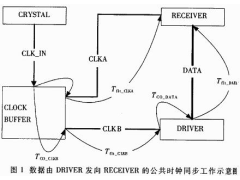

写在前面: 由于不是每个项目要求时间精度达到ns级,因此做同步电路的时候可以忽略很多设计因素.但是导致同步电路出现故障的原因,却大都是没有考虑同步电路的典型 特性和规则.作为新手,如果想从初步设计开始向进阶迈进,推荐阅读以下的文字.文章也许不一定100%正确,但是值得细细推敲和消化,有耐心的应该能有收获. 硕士博士可以 ..

[查看全文]

protues中把原理图转化为PCB图

2012-12-23

凡星

75

1、首先在isis中画好你的电路图,之后点击isis中tools/netlist compiler工具,弹出Netlist compiler对话框,点击ok,保存你的sdf文件。 2、打开Ares,load netlist file。左击鼠标,place所有的元器件,摆放好之后,呵呵,你想手动布线呢,这个不说了,自动布线呢,tools/auto router..ok 当然,你想快的话,alt+a,马上可以自动生 ..

[查看全文]

Protel DXP PCB的高级编辑技巧

2012-12-22

55

对于不同要求的 PCB 电路设计, Protel DXP 提供了一些高级的编辑技巧用于满足设计的需要,主要包括放置文字、放置焊盘、放置过孔和放置填充等组件放置,以及包地、补泪滴、敷铜等 PCB 编辑技巧。 这些编辑技巧对于实际电中板设计性能的提高是很重要的,本章将对这些编辑技巧进行详细说明。 7.1 放置坐标指示 放置坐标指示可以 ..

[查看全文]

高速PCB设计中的一些问题

2012-12-21

14

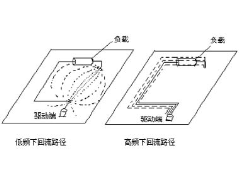

随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成为传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具和互连工具可以帮助设计师解决部分难题,但高速PCB设计也更需要经验的不断积累及业界间的深入交流。布线拓扑对信号完整性的影响当信号在高速PCB板上沿传 ..

[查看全文]

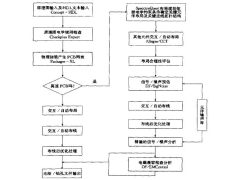

PowerPCB电路板设计规范

2012-12-21

21

1 概述 本文档的目的在于说明使用PADS的印制板设计软件PowerPCB进行印制板设计的流程和一些注意事项,为一个工作组的设计人员提供设计规范,方便设计人员之间进行交流和相互检查。 2 设计流程 PCB的设计流程分为网表输入、规则设置、元器件布局、布线、检查、复查、输出六个步骤. 2.1 网表输入 网表输入有两种方法,一种是 ..

[查看全文]

高速PCB设计的叠层问题

2012-12-20

Ming

9

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在多层板的设计中,对于叠层的安排显得尤为重要。一个好的叠层设计方案将会大大减小EMI及串扰的影响,在下面的讨论中,我们将具体分析叠层设计如何影响高速电路的电气性能。 一.多层板和铺 ..

[查看全文]

ORCAD传递分立器件Value值到PowerPCB的方法

2012-12-19

13

借助PCBNavigator,ORCAD与PowerPCB实现了很好的同步操作,但遗憾的是器件的Value值不能传递到PowerPCB,给人的感觉是ORCAD不如Powerlogic。经本人的摸索,找到了一种非常简单的办法,可以实现此功能。 1. 填写ORCAD的封装,即Footprint,此处必须填PowerPCB库中的Decal,而不是Part。 2. 在Orcad的Project M ..

[查看全文]

Cadence EDA中PCB分析工具Specctraquest的使用

2012-12-18

李玉蓉

16

电子设计自动化(EDA)技术是目前进行电子产品设计中所采用的主要技术.设计者利用它可以设计出更完美的产品,并且极大地缩短了设计周期。但是随着电子技术的不断发展,在设计中,特别是在高速PCB的设计中出现了一些新的问题。例如:延时、串扰、电磁干扰等物理设计问题,迫切需要提供一些仿真分析工具来解决这些问题。本文 ..

[查看全文]

推荐文章

最新文章

热门文章