TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

12

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

可以在Keil下仿真的T9拼音输入法

2012-06-02

37

/*特点是直接在Keil下仿真,切换到串口窗口就可以直接看到结果。 体验仿真步骤如下: 1、把3个帖子的内容分别保存为51t9py.c,51t9py_indexa.h,5py_mb.h,放在同一目录下,将51t9py.c加入工程编译 2、由于Keil的模拟串口是单字节显示,汉字显示为乱码,所以要加挂RICHWIN或RichView这种会重新刷新显示的中文平台,或手工刷 ..

[查看全文]

基于PSPICE的555定时器电路仿真分析

2012-06-02

郭文强 侯勇严

27

摘要:555定时器作为应用广泛的一种数字一模拟混合集成电路,其原理分析比较复杂。作者在文中应用PSPICE对555定时器构成的施密特触发器、单稳态触发器和多谐振荡器的工作特性进行了仿真分析和研究,针对PSPICE 中555定时器构成的多谐振荡器不起振的问题提出了模拟振荡电路的有效起振方法,对电子电路的分析与设计具有一定 ..

[查看全文]

利用ModelSim SE6.0C实现时序仿真

2012-06-02

12

1) 打开一个工程文件。 2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。在右边出现的设置栏中将“Tool name”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择 ..

[查看全文]

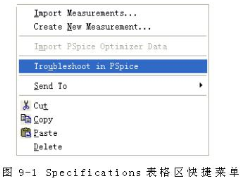

从实例中学习OrCAD-PSpice 10.3-AA(第9章 仿真的故障排...

2012-06-02

41

第9章 仿真的故障排除 在运行高级分析工具的过程中,由于操作失误、参数设置不合理等方面的原因,常常出现错误信息或者系统仿真不能运行等情况,用户往往得不到理想的分析结果,面对这些存在的难题,不能坐着发闷,要积极的解决问题。本章主要介绍运用故障排除分析工具解决存在问题的使用方法及高级分析中一般性故障的解决方 ..

[查看全文]

MultiSIM 电子仿真软件使用技巧

2012-06-02

朱秋龙

120

众所周知,电子仿真软件MultiSIM最初由加拿大的IIT 公司推出,从Multisim2001开始到后来的Multisim7和Multisim8止;Multisim9到目前的Multisim10版本,已改由美国国家仪器公司(NI公司)所推出。Multisim版本每次升级,软件功能都有相应的提高,但它们的操作方法和电子电路虚拟仿真这一块内容几乎没有太大的变化。也就是说 ..

[查看全文]

使用compxlib命令编译Xilinx的ModelSim仿真库

2012-06-02

20

ModelSim是Mentor Graphics出品的一款VHDL、Verilog、SystemC、SystemVerilog以及混合语言设计的仿真和验证工具。在ModelSim中,所有的设计(包括用户设计以及EDA工具预先提供的设计)必须编译成一个或多个仿真库。ModelSim的仿真库实际是一个目录,它可以看作是存储经过编译的设计单元的“仓库”。Mod ..

[查看全文]

80C51 系列单片机仿真器选购指南

2012-06-02

17

第一章为什么要使用仿真器? 1.1 仿真的概念 仿真的概念其实使用非常广,最终的含义就是使用可控的手段来模仿真实的情况。 在嵌入式系统的设计中,仿真应用的范围主要集中在对程序的仿真上。例如,在单片机的开发过程中,程序的设计是最为重要的但也是难度最大的。一种最简单和原始的开发流程是:编写程序-烧写芯片-验证功能 ..

[查看全文]

Cadence 仿真流程

2012-06-02

Poqi055

61

第一章 在Allegro 中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 使用SpecctreQuest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面 ..

[查看全文]

我的仿真工作流程(Verilog/Modelsim+Debussy)

2012-06-02

25

这是献给大家的第二篇,文章详细说明了本人近一年来,自己摸索出来的一套仿真工作流程。接触过Modelsim这类软件的朋友可能都会感觉上手比较困难,原因有二:一、对仿真机制不了解,对基于source+testbench的工作流程不熟悉(大多数朋友接触FPGA仿真可能以waveform的方式);二、对软件的安装和使用不熟悉,Modelsim软 ..

[查看全文]

时序计算和Cadence仿真结果的运用

2012-06-02

余昌盛 刘忠亮

10

摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。 一、前言 通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真 ..

[查看全文]

Multisim 10仿真实验

2012-06-02

10

一、 实验目的 熟悉并掌握Multisim10对单片机的仿真过程。 加深对单片机硬件以及软件理论知识的理解。 二、 实验原理 1、Multisim10 美国国家仪器公司下属的ElectroNIcs Workbench Group在今年年初发布了Multisim 10。新版的Multisim10,加入了MCU模块功能,可以和8051等单片机进行编程联调,该软件元件丰富,界面直观,虚拟 ..

[查看全文]

推荐文章

最新文章

热门文章