fir滤波器的Verilog程序

2012-06-02

31

`timescale 1ns / 1ps //////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date:17:01:38 10/09/06 // Design Name: // Module Name:ppeifir // Project Name: // Target Device: // Tool versions: // Description:用Verilog编写的fir滤波器程 ..

[查看全文]

SPI串行总线接口的Verilog实现

2012-06-02

孙丰军 余春暄

15

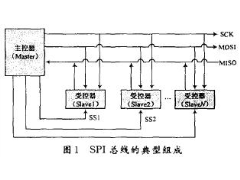

摘 要:集成电路设计越来越向系统级的方向发展,并且越来越强调模块化的设计。SPI(Serial Peripheral Bus)总线是Motorola公司提出的一个同步串行外设接口,容许CPU 与各种外围接口器件以串行方式进行通信、交换信息。本文简述了SPI总线的特点,介绍了其4条信号线,SPI串行总线接口的典型应用。重点描述了SPI串行总线接口在一款 ..

[查看全文]

用Verilog HDL设计自动数据采集系统

2012-06-02

10

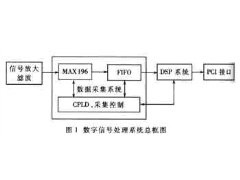

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

Verilog-HDL仿真软件ModelSim的基本操作

2012-06-02

常晓明

10

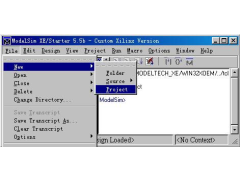

Verilog-HDL与CPLD/FPGA设计应用讲座 第 4 讲 Verilog-HDL仿真软件的基本操作 4.1 建立新的工程文件 4.2 一个最简单的仿真实例 在本讲以Xilinx WebPACK 4.1 ModelSim XE Starter为例,说明仿真软件的基本操作。 4.1 建立新的工程文件 启动Xilinx WebPACK 4.1 ModelSim XE Starter后,选中【File】菜单中的【New】菜单项, ..

[查看全文]

SystemVerilog语言简介

2012-06-02

39

SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、 接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera开发,它主要定位在芯片的 ..

[查看全文]

Verilog脉冲发生器程序

2012-06-02

万雪松

24

/*************************************************************************************** 实现功能简述 本模块主要功能是产生一个确定时钟周期长度(最长为256个时钟周期)的脉冲信号,可以自己设定脉冲长度,输出的脉冲信号与时钟上升沿同步 脉冲宽度 = pulsewide + 1 时钟周期; 输入一个启动信号后,可以产生一个 ..

[查看全文]

推荐文章

最新文章

热门文章