从实例中学习OrCAD-PSpice 10.3-AA(第二章 OrCAD 10.3...

2012-06-02

14

OrCAD10.3是OrCAD a Cadence product family 公司于2004年11月推出的电子设计自动化(EDA)软件系统。其中包括三个主要部分: 锁定元件信息系统的原理图输入器(Capture CIS); 模拟和混合信号仿真(PSpice A/D)和其高级分析(PSpice –AA); 印刷电路板设计(Layout Plus)形成Gerber文件可与Protel等PCB软 ..

[查看全文]

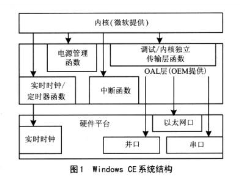

Windows CE OAL层的结构与开发

2012-06-02

齐晓静 王卫东 王剑

7

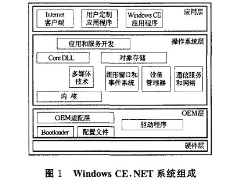

Windows CE微软针对嵌入式领域推出的一款全新的操作系统。之所以说它是一款全新的操作系统,是因为尽管Windows CE的UI非常接近其它的桌面版Windows操作系统,但是它的内核完全是重新写的,并不是任何一款桌面版Windows的精简版本。 Windows CE是一种支持多种CPU架构的操作系统,其中包括ARM、x86、MIPS和SHx,极 ..

[查看全文]

用AXD 和Multi-ICE调试uClinux内核

2012-06-02

7

AXD Multi-ICE进行裸机程序调试的功效相信已经为大家所接受。uClinux内核比较裸机程序,有较大的不同。这里简单介绍如何用AXD源代码级调试uClinux内核。 所提到的uClinux版本是uClinux-dist-20030522.tar.gz,并且已经使用了www.dailzh.net上提供的patch。并且我有义务告诉您,这一调试方法可行,但尚需要完善。 步骤一: ..

[查看全文]

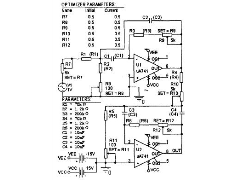

基于PSPICE的555定时器电路仿真分析

2012-06-02

郭文强 侯勇严

27

摘要:555定时器作为应用广泛的一种数字一模拟混合集成电路,其原理分析比较复杂。作者在文中应用PSPICE对555定时器构成的施密特触发器、单稳态触发器和多谐振荡器的工作特性进行了仿真分析和研究,针对PSPICE 中555定时器构成的多谐振荡器不起振的问题提出了模拟振荡电路的有效起振方法,对电子电路的分析与设计具有一定 ..

[查看全文]

Cadence产品的介绍

2012-06-02

12

Cadence公司是一家eda软件公司。成立于1988年。其主要产品线从上层的系统级设计到逻辑综合到低层的布局布线,还包括封装、电路版pcb设计等等多个方向。下面主要介绍其产品线的范围。 1、板级电路设计系统 。 包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计 ..

[查看全文]

基于PSpice的四阶有源带通滤波器的统计优化设计

2012-06-02

汪汉新 喻胜辉

21

PSpice作为功能强大的EDA电子仿真软件,不仅能对电路进行基本性能的分析和验证,还可以进行优化分析和综合统计分析,实现从电路的设计、性能分析、参数优化到电路板制作的全过程,因此它在电路的设计中得到广泛地应用.本文针对电子产品在实际生产过程中由于元器件参数值的随机分布性而造成产品合格率下降的问题,在分析PS ..

[查看全文]

Cadence 仿真流程

2012-06-02

Poqi055

61

第一章 在Allegro 中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 使用SpecctreQuest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面 ..

[查看全文]

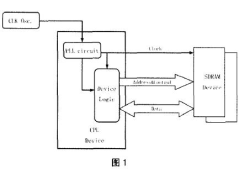

时序计算和Cadence仿真结果的运用

2012-06-02

余昌盛 刘忠亮

10

摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。 一、前言 通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真 ..

[查看全文]

嵌入式操作系统Windows CE.NET在S3C2410平台上的移植

2012-06-02

丁玉芳 李允俊

11

因为嵌入式系统的环境要求,嵌入式操作系统一般需要提供可添加或可裁减的内核及其他功能,以能够让用户根据需要进行配置.目前,嵌入式微处理器种类很多,嵌入式操作系统要支持尽可能多的处理器,这就要完成操作系统针对不同处理器的定制. 本文分析了嵌入式操作系统Windows CE.NET的特点,并利用工具Platform Builder 4.2完 ..

[查看全文]

Cadence的 EDA验证工具在 SOC设计中的应用

2012-06-02

叶 辉

11

摘要: 本文介绍了Cadence公司的NC-Verilog/Verilog-XL Simulator以及Signalscan在SOC设计中的应用。 关键词: SOC,协同验证(co-verification) 在ASIC 和 SOC 设计中,验证是极为重要的一环,Cadence公司的NC-Verilog仿真器(以及较早产品 Verilog-XL)是用来仿真用 Verilog 语言写的数字逻辑电路。该仿真器在 ASIC和SO ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第6章 蒙特卡洛工具...

2012-06-02

32

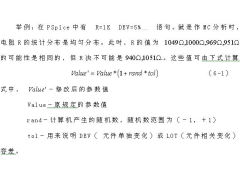

第6章 蒙特卡洛(Monte Carlo)工具的使用 PSpice一直重视所设计的电路,要能适合于批量生产的需要。现在PSpice10.3单独设立Monte Carlo工具,使这一项工作得到加强。本章先简介容差分析的基本概念,其后重点介绍Monte Carlo工具的使用方法。 6.1容差分析 前几章所述电路分析法时,已经提过只将元件视作理想元件按标称值进 ..

[查看全文]

从实例中学习OrCAD-PSpice 10.3-AA(第4章灵敏度分析工具)

2012-06-02

18

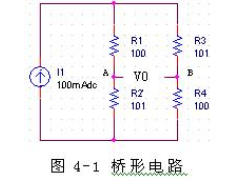

想要调用PSpice–AA进行电路优化设计,一般是先进行灵敏度(Sensitivity)分析:以便确定电路中对电路特性影响最大的关键元件参数进行优化。OrCAD9.2以前版本的灵敏度分析,由于有大量数据输出问题没有解决,故只局限于作直流灵敏度分析,置于直流工作点分析内。 直流灵敏度分析:虽然电路特性完全取决于电路中的元器 ..

[查看全文]

推荐文章

最新文章

热门文章