SDRAM控制器软核的Verilog设计

2012-11-23

18

目前,在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度高的存储器。在各种随机存储器件中,SDRAM 的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制逻辑复杂,使用很不方便。为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使 ..

[查看全文]

verilog HDL 的阻塞和非阻塞语句分析

2012-11-14

e人

10

在FPGA设计中完全透视verilog HDL 的阻塞和非阻塞语句,是个人在verilog HDL运用中的一些心得体会。 阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别。理解不清 ..

[查看全文]

Verilog HDL设计练习进阶(四)

2012-11-08

8

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别 目的:1.明确掌握阻塞赋值与非阻塞赋值的概念和区别; 2.了解阻塞赋值的使用情况。 阻塞赋值与非阻塞赋值,在教材中我们已经了解了它们之间在语法上的区别以及综合后所得到的电路结构上的区别。在always块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以 ..

[查看全文]

典型逻辑电路的Verilog-HDL描述

2012-11-06

常晓明 李媛媛

10

Verilog-HDL与CPLD/FPGA设计应用讲座 第 5 讲 典型基本逻辑路的Verilog-HDL描述 5.1 数据选择器 5.2 编码器 5.3 同步RS触发器 5.4 带有复位端的同步D触发器 本讲列举几个典型又简单的基本逻辑电路的Verilog-HDL描述。需要说明,仅有本讲的知识还不能具备用Verilog-HDL描述逻辑电路和系统的基本功,但却可以通过几个例子了解 ..

[查看全文]

VHDL设计中电路优化问题

2012-11-06

王春玲

10

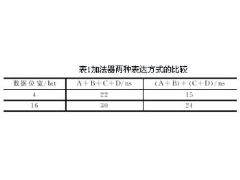

近年来,随着集成电路技术和EDA技术的不断发展,集设计、模拟、综合和测试功能为一体的VHDL语言,已作为IEEE标准化的硬件描述语言。由于其在语法和风格上类似于现代高级汇编语言,具有良好的可读性,描述能力强,设计方法灵活,易于修改,又具有可移植性,可重复利用他人的IP模块 (具有知识产权的功能模块)等诸多优势而成为 ..

[查看全文]

VHDL设计中电路简化问题的探讨

2012-11-05

13

近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级的设计?熕?带来的问题是设计者的设计思考与电路结构相脱节。设计者主要是根据VHDL的语法规则对系统目标的逻辑行 ..

[查看全文]

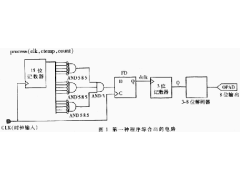

用VHDL语言设计延时电路

2012-11-02

13

用VHDL语言设计延时电路时一般用计数器或计数器的级联来实现。 下面以一个实例来说明如何实现任意时间量的延时。 在5 MHz时钟CLK控制下对同步信号SYNC进行N延时(SYNC脉冲宽度为2 μs,脉冲重复频率为1 kHz;0μs≤N≤998 μs)。要求每次在同步脉冲上升沿到来时开始延时,并在延时结束后产生宽度为10 μ ..

[查看全文]

用VHDL在CPLD上实现串行通信

2012-10-31

14

随着EDA技术得发展,CPLD已经在许多方面得到了广泛应用,而串行通信是实现远程测控的重要手段。本文利用VHDL语言在CPLD上实现了串行通信,完全可以脱离单片机使用,克服了单片机的许多缺点。 串口结构及内容 本设计所采用的是异步通信方式,可以规定传输的一个数据是10位,其中最低位为启动位(逻辑0低电平),最高位为停止位(逻 ..

[查看全文]

让Verilog仿真状态机时可以显示状态名

2012-10-31

RickySu

29

Situation: 我们平时使用Verilog进行状态机编码时,通常使用parameter对状态名进行定义,这样写Case语句的时候就不会对这一串10摸不着头脑。可是通常这样做的话,在Modelsim里看到的还是一串10,使排错非常困难,特别是在用OneHot编码的时候,就看到一串0中间的一个1 #_# 简直要疯掉。 Question: 我们可不可以像VHDL一样 ..

[查看全文]

Verilog-HDL与CPLD/FPGA设计

2012-10-31

常晓明

38

Verilog-HDL与CPLD/FPGA设计应用讲座 第 1 讲 Verilog-HDL与CPLD/FPGA设计 1.1 从模拟世界到数字世界 1.2 数字电路的不同设计过程 1.3 用HDL描述数字电路 1.4 HDL有几种? 1.5 硬件实现的承担者---CPLD/FPGA 1.6 Xilinx公司的CPLD--XC9500系列 1.7 结语 1.1 从模拟世界到数字世界 在70年代初期,家用电子产品末过于晶体管 ..

[查看全文]

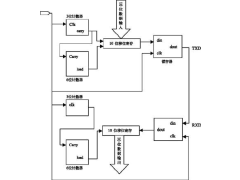

数字信号发送和接收的VHDL源码

2012-10-30

14

【数字信号的发送和接收】:设计一个5位数字信号的发送和接收电路,把并行码变为串行码或把串行码变为并行码,串行偶校验检测器可通过异或实现。在数据接收端,只有在代码传送无误后,才把数据代码并行输出。数据传送的格式采用异步串行通信的格式,包含起始位、数据位、校验位、停止位和空闲位。 数据发送模块:将并行数据加 ..

[查看全文]

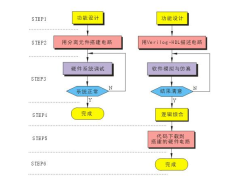

有限状态机的VHDL优化设计

2012-10-29

洪国玺 董辉

13

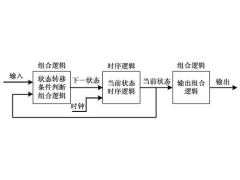

1.引言 当前以硬件描述语言为工具、逻辑器件为载体的系统设计越来越广泛。在设计中,状态机是最典型、应用最广泛的电路模块,其在运行速度的高效、执行时间的确定性和高可靠性方面都显现出强大的优势。状态机及其设计技术水平决定了系统设计的优劣[1]。如何设计一个最优化的状态机是我们必须面对的问题。 本文将详细讨论状态 ..

[查看全文]

推荐文章

最新文章

热门文章