VHDL 编程的一些心得体会

2012-06-02

6

VHDL 是由美国国防部为描述电子电路所开发的一种语言,其全称为(Very High Speed Integrated Circuit) Hardware Description Language。 与另外一门硬件描述语言 Verilog HDL 相比,VHDL 更善于描述高层的一些设计,包括系统级(算法、数据通路、控制)和行为级(寄存器传输级),而且 VHDL 具有设计重用、大型设计能力、 ..

[查看全文]

VHDL设计中的电路简化问题

2012-06-02

10

摘 要 :从描述方法、设计规则、逻辑函数分析了VHDL设计中容易引起电路复杂化的原因,并提出了相应的解决方法。 近年来,随着集成电路技术的发展,用传统的方法进行芯片或系统设计已不能满足要求,迫切需要提高设计效率。在这样的技术背景下,能大大降低设计难度的VHDL设计方法正越来越广泛地被采用。但是VHDL设计是行为级 ..

[查看全文]

用VHDL设计乐曲发生器

2012-06-02

姜田华

13

1 概述随着EDA 技术的进展,基于可编程 ASIC 的数字电子系统设计的完整方案越来越受到人们的重视,并且以 EDA 技术为核心的能在可编程 ASIC 上进行系统芯片集成的新设计方法,也正在快速地取代基于 PCB板的传统设计方式。 与利用微处理器(CPU 或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不 ..

[查看全文]

锁存器 vhdl源程序

2012-06-02

9

锁存器 vhdl Library IEEE ; use IEEE.std_logic_1164.all ; ENTITY latchinf IS PORT ( enable, data : IN BIT; q : OUT BIT ); END latchinf; ARCHITECTURE maxpld OF latchinf IS BEGIN latch : PROCESS (enable, data) BEGIN IF (enable = '1') THEN q END IF; END PROCESS latch; END maxpld;

[查看全文]

半整数分频的VHDL程序

2012-06-02

9

想出了一个半整数分频的VHDL语言描述 其实很多问题只要你耐心,也是比较容易的 写出来与大家共享,共同讨论,半整数分频当然还有其他的方法 我认为这种看起来蛮简单的 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity abc is port(clk:in std_logic; dout:out std_logic); end abc; architecture x ..

[查看全文]

汽车车灯控制系统的VHDL语言实现

2012-06-02

郑应民

7

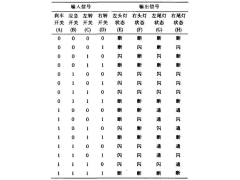

当前数字电路系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。利用大规模可编程逻辑器件CPLD(Complex Programmable Logic Device)进行ASIC设计,可以直接面向用户需求,根据对系统的功能要求自上而下地逐层完成相应的描述、综合、优化、仿真与验证,直到生成元器件。目前,系统级的仿真工具也已出现.这样可以大 ..

[查看全文]

VHDL语言程序配置EAB的研究

2012-06-02

何永泰

20

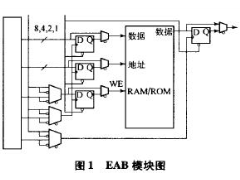

摘要: 在FPGA(现场可编程门阵列)的使用中,要将VHDL(甚高速集成电路硬件描述语言)编写的程序配置到EAB(嵌入式阵列块)单元中,会遇到许多问题,配置很难成功。根据配置EAB的经验,详细介绍了正确配置EAB的方法。 1、引言 FLEX10K器件是工业界第一个嵌入式的PLD(可编程逻辑器件),由于其具有高密度、低成本、低功率等特点,成 ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

12

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

debussy和modelsim协同仿真(VHDL)

2012-06-02

18

1、 编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。 2、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中 3、 将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录 4、 ..

[查看全文]

SVPWM信号发生器的VHDL实现

2012-06-02

吴晨光

9

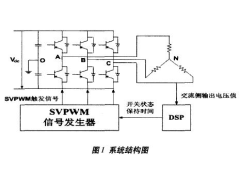

近年来,DSP在SVPWM(空间矢量脉宽调制)控制领域得到了广泛应用。但是使用DSP单核心的控制方法仍然存在一些缺陷:基于软件的:DSP在实现SVPWM触发信号时需要较长的时钟周期;微处理器中不确定的中断响应会导致PWM脉冲的相位抖动。针对以上问题,本文提出了一种利用FPGA实现的SVPWM信号发生器,系统结构如图1所示 ..

[查看全文]

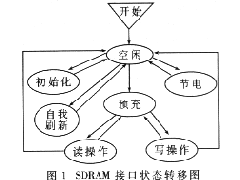

SDRAM接口的VHDL设计

2012-06-02

沙燕萍 曾烈光

18

SDRAM接口的VHDL设计 RAM(随机存取存储器?犑且恢衷诘缱酉低持杏τ霉惴旱钠骷?,通常用于数据和程序的缓存。随着半导体工业的发展,RAM获得了飞速的发展,从RAM、DRAM(Dynamic RAM,即动态RAM)发展到SDRAM(Synchronous Dynamic RAM,即同步动态RAM),RAM的容量越来越大、速度越来越高,可以说存储器的容 ..

[查看全文]

ADC0809 VHDL控制程序

2012-06-02

39

--文件名:ADC0809.vhd --功能:基于VHDL语言,实现对ADC0809简单控制 --说明:ADC0809没有内部时钟,需外接10KHz~1290Hz的时钟信号,这里由FPGA的系 --统时钟(50MHz)经256分频得到clk1(195KHz)作为ADC0809转换工作时钟。 --最后修改日期:2004.3.20 library ieee; use ieee.std_logic_1164.all; use ieee.std ..

[查看全文]

推荐文章

最新文章

热门文章