modelsim学习笔记

2012-10-10

16

1. 建一个总文件夹,如cnt 2. 为源代码,测试台文件,仿真各建一文件夹。如src,tb,sim 3. 编写源代码,testbench。如cnt.v,tb_cnt.v文件,同时文件名里的模块名与文件名相同,如modulecnt(), moduletb_cnt()。 4. 再sim文件夹里加入tb.f文件:../tb/tb_cnt.v ../src/cnt.v ../tb/tb_cnt-y ../src+libext+.v(这里源代码 ..

[查看全文]

Modelsim 包会教程

2012-10-10

Timothy.Lee

10

Modelsim是现在业界比较流行的HDL语言仿真工具。在这里关于他的使用我就不说了。主要是讲一讲困扰我们的库编译的问题。 因为Modelsim为各个主要fpga厂商都提供了支持,所以在我们使用的时候必须先要对相应的厂商的库进行编译。在这里,我以xilinx公司为例。使用的软件为ise5.2i,modelsim se 5.7c(如果版本不同,并不影响 ..

[查看全文]

ModelSim SE操作指南

2012-07-03

29

第一章 介绍 本指南是为 ModelSim5.5f版本编写的,该版本运行于UNIX和Microsoft Windows 95/98/Me/NT/2000的操作系统环境中。本指南覆盖了VHDL和Verilog模拟仿真,但是你在学习过程中会发现对于单纯的HDL设计工作而言,它是一个很有用的参考。ModelSim具备强大的模拟仿真功能,在设计、编译、仿真、测试、调试开发过 ..

[查看全文]

modelsim仿真问题

2012-06-02

84

近段时间比较忙,尝试着将工作中碰到的问题记录下来,也许它在某一天它会变成一笔财富了?不管怎么说,尝试记录工作的点滴都是一个不错的点子,呵呵。夸奖一下我自己! 在用modelsim 6.0 se作仿真的时候碰到一个错误,在xilinx的数据库里面发现原因如下: Problem Description: Keywords: ModelSim, MXE, MTI, error, VSIM ..

[查看全文]

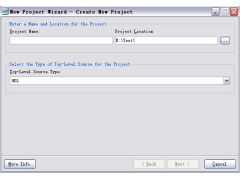

ModelSim SE 快速入门

2012-06-02

16

本文以ModelSim SE 5.6版本为基础,介绍ModelSim SE的最基本用法,高深的我也不会 。 当你安装完ModelSim SE之后,可以将你的ModelSim SE的起始路径设置为你的工作目录(如e:\verilog),具体方法是在右键单击执行文件ModelSim SE的图标再点击属性栏,就可以看到ModelSim SE的起始位置,改为你的工作目录就可。 学习ve ..

[查看全文]

ModelSim作布局布线后仿真的库问题

2012-06-02

12

Modelsim是目前最流行的应用最广泛的FPGA仿真器,是Mentor Graphics的子公司Model Technology开发的。因为Modelsim好学易用,调试方便,仿真速度快,功能强大,所以很多芯片厂商的开发系统都OEM Mentor Graphics公司的Modelsim仿真器,包括Xilinx,Altera,Lattice和Actel等。Modelsim是一个单内核仿真器,同一个内 ..

[查看全文]

ModelSim下用SystemC做设计验证方法与示例

2012-06-02

12

最近用SystemC做验证做上瘾了,写一个小文吧。 如何在ModelSim下编译和仿真SystemC的设计? 如何在ModelSim下用SystemC的做验证? SystemC作为一种系统级设计与验证语言,非常适合做复杂IC的验证,而不是用于RTL描述。很多人问我如何将SystemC综合和编译为可以下载的CPLD/FPGA的比特文件或者综合为ASIC网表,我的 ..

[查看全文]

怎样用modelsim做后仿真

2012-06-02

18

怎样用modelsim做后仿(编译工具采用quatus) step1: 在qurtus改变编译选项: assignments->EDA tool setting:选择verilog还是vhdl。 step2: 编译。你会在你的工程所在目录 看到一个simulation的目录,这里面有你生成的网表文件和标准延时文件。 step3: 在目录:\quartus\eda\sim_lib找到你选用器件对应的库文件,将库文件 ..

[查看全文]

使用compxlib命令编译Xilinx的ModelSim仿真库

2012-06-02

20

ModelSim是Mentor Graphics出品的一款VHDL、Verilog、SystemC、SystemVerilog以及混合语言设计的仿真和验证工具。在ModelSim中,所有的设计(包括用户设计以及EDA工具预先提供的设计)必须编译成一个或多个仿真库。ModelSim的仿真库实际是一个目录,它可以看作是存储经过编译的设计单元的“仓库”。Mod ..

[查看全文]

modelsim for linux安装指南

2012-06-02

18

for modelsim: 1 下载modelsim for linux的下载文件。应该总共有三个文件,分别是base,docs和linux.exe。都是gz压缩的。 2 解压缩linux.exe,解出来的是可以在终端中直接运行的文件,运行之,并安装。 3 分别解压base和docs在同一目录下。 4 把这时候的modeltech目录(也就是解压缩和安装后形成的目录)移动到你希望程序所存放 ..

[查看全文]

ModelSim se完全编译Xilinx库文件

2012-06-02

16

什么是之前的老办法呢? Modlesim 仿真库的建立: 将Modelsim根目录下的modelsim.ini的属性由只读改为可写。 新建一个文件夹,比如library(为叙述方便,把它放在modelsim的根目录下)。D:/modelsim/library. 启动Modelsim,选择[File]/[chang Directory],选择D:/modelsim/library. 选择[File]/[New]/[library]命令,弹出[C ..

[查看全文]

Xilinx FPGA开发环境的配置

2012-06-02

风子心

20

一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录; C、运行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根据你安装的modelsim目录 ..

[查看全文]

推荐文章

最新文章

热门文章