状态机性能考察(状态编码)

2012-10-04

14

最近对状态机产生了兴趣。看了老外的文章才知道这个领域真是旷阔无边,他们做学问的态度实在是扎实。所以先做个读书笔记。 状态机的性能指标太多,我能力有限,目前在考察范围内的只有所需的逻辑资源和简单的时序特性两项指标。 影响一个状态机的性能有多个因素,包括状态集合的编码、状态机的HDL编写方式、所采用的器件结构, ..

[查看全文]

自动售货机控制系统VHDL有限状态机实现

2012-06-13

赖义汉

10

1 引言 有限状态机FSM(Finite State Machine)及其设计技术是实用数字系统设计中实现高效率、高可靠逻辑控制的重要途径。传统的状态机设计方法需进行繁琐的状态分配、绘制状态表、化简次态方程等,而利用VHDL可以避免这些繁琐的过程,直接利用状态转换图进行状态机的描述,所有的状态均可表达为CASE_WHEN结构中的一条CA ..

[查看全文]

Verilog HDL代码描述对状态机综合的研究

2012-06-02

李玲 王祖强 陈东海

5

1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元 ..

[查看全文]

mealy&moore状态机典型程序

2012-06-02

11

Verilog // Example of a 5-state Mealy FSM module mealy (data_in, data_out, reset, clock); output data_out; input [1:0] data_in; input reset, clock; reg data_out; reg [2:0] pres_state, next_state; parameter st0=3'd0, st1=3'd1, st2=3'd2, st3=3'd3, st4=3'd4; // FSM register always @ (posedge clock or ..

[查看全文]

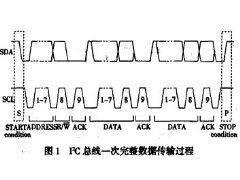

FPGA有限状态机模拟I2C总线设计

2012-06-02

潘小冬

15

摘要:以I2C总线协议为根据。用有限状态机(FSM:Finite State Machine)设计了基于FPGA的I2C初始化程序模块。主要内容包括简述I2C总线的特点;介绍用FPGA中FSM开发I2C总线模块时的设计思想和实现过程;给出并解释了部分用Verilog HDL描述I2C总线初始化SAA7111和SAA7121的程序,最后在QuartusII中进行了I2C总线主从模 ..

[查看全文]

利用有限状态机控制A/D采样

2012-06-02

13

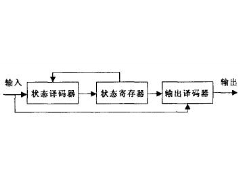

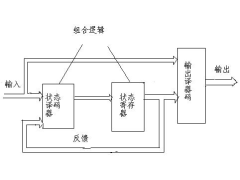

1 状态机的基本结构和功能 状态机是一类很重要的时序电路,是许多数字电路的核心部件。状态机的一般形式如图1所示。除了输入信号、输出信号外,状态机还包括一组寄存器,它用于记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还于寄存器当前状态有关。寄存器可以认为是组合逻辑和寄存器逻辑 ..

[查看全文]

推荐文章

最新文章

热门文章