如何搭建Xilinx FPGA开发环境

2012-06-02

风子心

5

一、计算机硬件环境要求 : 1、操作系统: Microsoft Windows XP Home Edition SP2 2、基本配置: A、处理器:Intel CPU T2050 1.6GHz B、内存:512MB C、硬盘:60GB(其中软件安装的空问需要3GB) 补充: 上面的配置为笔记本的配置。因此对显卡没有什么特殊的要求。有条件的话,尽可能选择更高的配置。这样软件跑起来会更快。 ..

[查看全文]

如何计算FPGA设计频率

2012-06-02

21

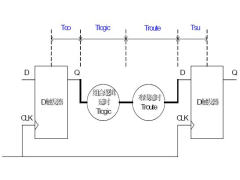

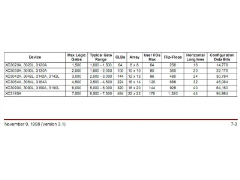

我们的设计需要多大容量的芯片?我们的设计能跑多快?这是经常困扰工程师的两个问题.对于前一个问题,我们可能还能先以一个比较大的芯片实现原型,待原型完成再选用大小合适的芯片实现.对于后者,我们需要一个比较精确的预估,我们的设计能跑50M,100M 还是133M? 首先让我们先来看看Fmax 是如何计算出来的.图(1)是一个通用的模 ..

[查看全文]

基于FPGA 的高阶全数字锁相环的设计与实现

2012-06-02

单长虹 王彦 陈文光 陈忠泽

6

摘要:提出了一种实现高阶全数字锁相环的新方法。该锁相环以数字比例积分控制取代了传统的一些数字环路滤波控制方法,具有电路结构简单、控制灵活、跟踪精度高、环路性能好和易于集成的特点。文中介绍了该高阶全数字锁相环的系统结构和工作原理,对其性能进行了理论分析和计算机仿真。应用EDA 技术设计了该系统,并用FPGA实 ..

[查看全文]

Altera FPGA、CPLD 学习笔记

2012-06-02

9

1.硬件设计基本原则 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用 & ..

[查看全文]

FPGA三国志-第一篇/不可不看的故事

2012-06-02

wisdomz

5

CPLD的时代 我在12年前,偶然接触PLD,没有想到自己居然就在这个行当里安身下来。可是这个行业也的确是个飞速发展的行业,十多年过去后,从当初的接近十家主要供应商,到今天已经激烈搏杀后,只有差不多如论坛题目一样的,成为了今天三足鼎立的局面。想来想去,决定以这个名字作为论坛的主题。同时也和大家分享我多年来的一 ..

[查看全文]

基于FPGA的多路脉冲重复频率跟踪器

2012-06-02

12

摘要:在反辐射导弹的雷达导引头中,信号跟踪器的实时性是影响系统性能的重要因素之一。介绍了利用高性能FPGA丰富的资源实现的多路脉冲重复频率跟踪器,它解决了在密集信号环境下信号跟踪的实时性问题,减小了系统体积。经过实验验证,其各项指标均达到了设计要求。 随着高科技的迅速发展,现代战争已经不仅是传统意义战场上 ..

[查看全文]

固定几何结构的FFT算法及其FPGA实现

2012-06-02

9

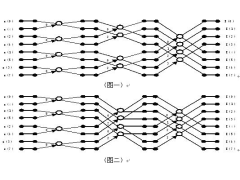

1.引言 DFT及其快速算法FFT是信号处理领域的核心组成部分。FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。各算法的优缺点视不同的制约因素而不同。FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。一般多结合 ..

[查看全文]

使用基于FPGA的硬件方法实现算法加速

2012-06-02

Lara Simsic

11

当设计者试图从算法中获得最佳性能但软件方法已无计可施时,可以尝试通过硬件/软件重新划分来进行加速。FPGA易于实现软件模块和硬件模块的相互交换,且不必改变处理器或进行板级变动。本文阐述如何用FPGA来实现算法的硬件加速。 如果想从代码中获得最佳性能,方法包括优化算法、使用查找表而不是算法、将一切都转换为本地 ..

[查看全文]

异步FIFO结构及FPGA设计

2012-06-02

7

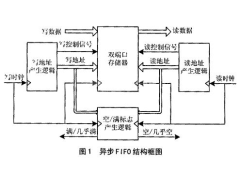

摘要 :首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA实现。 1、异步FIFO介绍 在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口 ..

[查看全文]

静态时序分析在高速FPGA设计中的应用

2012-06-02

周海斌

27

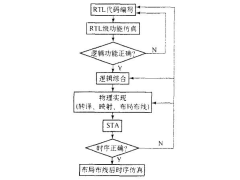

摘要:介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进时序收敛的方法。结合设计实例,阐明了STA在高速、大规模FPGA开发中的应用。实践表明,随着数字设计复杂度的增加,在后端的时序验证环节,与传统的动 ..

[查看全文]

基于FPGA的逆变器全数字锁相环设计

2012-06-02

罗旭 占荣 康勇

30

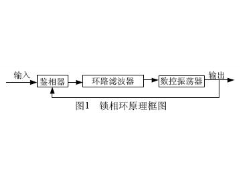

摘要:文章设计了一种可应用于逆变器的、用FPGA 实现的二阶全数字锁相环(DPLL)。此锁相环用比例积分方法替代传统锁相系统中的环路滤波(LF),用相位累加器实现数控振荡器(DCO)的功能。具有输出相位连续、分辨率高等优点。分析了它的原理和结构,给出了关键部件的verilog 代码及仿真结果。仿真结果表明了设计的正确性 ..

[查看全文]

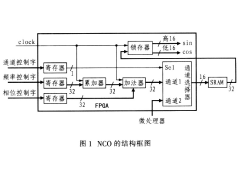

基于FPGA和SRAM的数控振荡器的设计与实现

2012-06-02

佟力永 肖山竹

8

1 、引言 数控振荡器是数字通讯中调制解调单元必不可少的部分,同时也是各种数字频率合成器和数字信号发生器的核心。随着数字通信技术的发展,对传送数据的精度和速率要求越来越高。如何得到可数控的高精度的高频载波信号是实现高速数字通信系统必须解决的问题,可编程逻辑器件和大容量存储器的发展为这一问题的解决带来了曙光 ..

[查看全文]

推荐文章

最新文章

热门文章