TEXTIO及其在VHDL仿真中的应用

2012-06-02

于红旗

12

TEXTIO 在VHDL 仿真与磁盘文件之间架起了桥梁,使用文本文件扩展VHDL 的仿真功能。本文介绍TEXTIO 程序包,以一个加法器实例说明TEXTIO 的使用方法,最后使用ModelSim 对设计进行仿真,并分析仿真结果。 在对VHDL 源程序进行仿真时, 由于有的输入输出关系仅仅靠输入波形或编写testbench 中的信号输入是难以验证结果正确 ..

[查看全文]

锁存器 vhdl源程序

2012-06-02

9

锁存器 vhdl Library IEEE ; use IEEE.std_logic_1164.all ; ENTITY latchinf IS PORT ( enable, data : IN BIT; q : OUT BIT ); END latchinf; ARCHITECTURE maxpld OF latchinf IS BEGIN latch : PROCESS (enable, data) BEGIN IF (enable = '1') THEN q END IF; END PROCESS latch; END maxpld;

[查看全文]

Verilog交通灯控制器程序

2012-06-02

5

交通灯控制器 /* 信号定义与说明: CLK: 为同步时钟; EN: 使能信号,为1 的话,则控制器开始工作; LAMPA: 控制A 方向四盏灯的亮灭;其中,LAMPA0~LAMPA3,分别控制A 方向的 左拐灯、绿灯、黄灯和红灯; LAMPB: 控制B 方向四盏灯的亮灭;其中,LAMPB0 ~ LAMPB3,分别控制B 方向的 左拐灯、绿灯、黄灯和红灯; ACOU ..

[查看全文]

基于VHDL的异步串行通信电路设计

2012-06-02

李刚强

13

1 引 言 随着电子技术的发展,现场可编程门阵列 FPGA和复杂可编程逻辑器件CPLD的出现,使得电子系统的设计者利用与器件相应的电子CAD软件,在实验室里就可以设计自己的专用集成电路ASIC器件。这种可编程ASIC不仅使设计的产品达到小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费 ..

[查看全文]

浅谈VHDL/Verilog的可综合性以及对初学者的一些建议

2012-06-02

12

一、HDL不是硬件设计语言 过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。在这个论坛上,也时常能看到一些网友提出这一类的问题。 对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。HDL是Har ..

[查看全文]

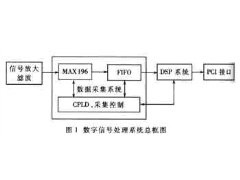

用Verilog HDL设计自动数据采集系统

2012-06-02

10

随着数字时代的到来,数字技术的应用已经渗透到了人类生活的各个方面。数字系统的发展在很大程度上得益于器件和集成技术的发展,著名的摩尔定律(Moore's Law)的预言也在集成电路的发展过程中被印证了,数字系统的设计理念和设计方法在这过程中发生了深刻的变化。从电子CAD、电子CAE到电子设计自动化(EDA ..

[查看全文]

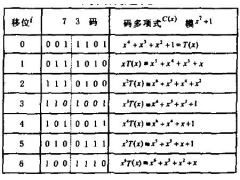

VHDL的CRC编码器的设计

2012-06-02

郑春来

28

CRC码是线性分组码的一个重要子集,它是为了保证通信系统中的数据传输可靠性而采取的信道编码技术。CRC码除了具有分组码的线性外,还具有循环性,其码字结构一般用符号(n,k)表示,其中,n是该码组中的码元数,k是信息码位数,r=n-k是监督码元位数。循环码具有许多特殊的代数性质,这些性质有助于按照要求的纠错能力系统地 ..

[查看全文]

Verilog代码编写规范

2012-06-02

11

一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师 ..

[查看全文]

VHDL设计的消抖与滤波

2012-06-02

13

在同一块电路板上,由于信号线的走线过长而产生的高频毛刺我们可以通过在接近输入端串联一个100欧左右的电阻来滤除。但是对于板外信号,或者板内其他干扰造成较大的抖动时只好采用积分电路来滤波,即串一个电阻还要并一个电容接地。 同样在VHDL中我们可以采用类似的办法,对于小于触发器建立时间的毛刺可以用时钟打一下实现 ..

[查看全文]

推荐文章

最新文章

热门文章