复用器重构降低FPGA成本

2012-06-02

11

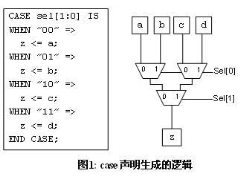

摘要 本文介绍了一种新的能够降低FPGA实际设计20%成本的综合算法。该算法通过减少复用器所需查找表(LUT)的数量来实现。算法以效率更高的4:1复用器替代2:1复用器树。算法性能关键在于寻找总线上出现的复用器数量。新的优化方法占用一定的逻辑,这些逻辑由总线进行分担,从而减少了总线上每个比特位所需的逻辑。 1.引言 复 ..

[查看全文]

基于FPGA的IIR数字滤波器的快捷设计

2012-06-02

童位理

16

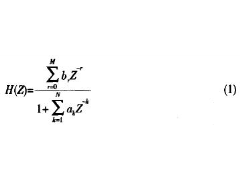

IIR数字滤波器在很多领域中都有着广阔的应用。与FIR数字滤波器相比,IIR数字滤波器可以用较低的阶数获得较高的选择性,而且所用存储单元少。经济效率高。一个N阶IIR数字滤波器的系统函数为: 其线性常系数差分方程为: 用FPGA实现滤波的基本思想就是基于式(2)来实现的。如果知道了系统的输入序列(滤波器的输入),那么,只要 ..

[查看全文]

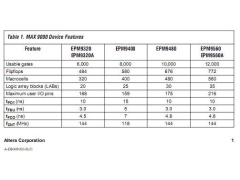

CPLD开发板和FPGA开发板的区别

2012-06-02

抽烟的鱼

16

市面上尤其是学校里面可以看到Xilinx公司或者Altera公司各种不同的开发板,其实只有两个大类,CPLD开发板和FPGA开发板。尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点: ①CPLD更适合完成各种组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富 ..

[查看全文]

基于FPGA的高速数据采集系统接口设计

2012-06-02

黄伟,罗新民

14

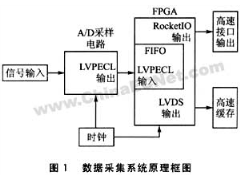

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理 ..

[查看全文]

IIR数字滤波器的FPGA实现

2012-06-02

魏国华

8

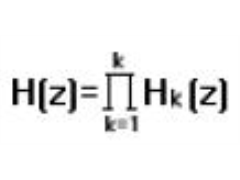

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此设计扩展性好,便于调节滤波器的性能,可以根据不同的要求在不同规模的FPGA上加以实现。 IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同 ..

[查看全文]

基于FPGA的FIR滤波器的实现

2012-06-02

郭继昌 向 晖 滕建辅 李香萍

13

摘 要: 提出了一种采用现场可编程门阵列器件 FPGA并利用窗函数法实现线性 FIR数字滤波器硬件电路的方案,并以一个十六阶低通 FIR数字滤波器电路的实现为例说明了利用Xilinx公司 XC4000系列芯片的设计过程。设计的电路通过软件程序进行了验证和硬件仿真,结果表明电路工作正确可靠,能满足设计要求。 关键词: FPGA FIR数字滤 ..

[查看全文]

FPGA实现信号延时的方法

2012-06-02

16

FPGA实现信号延时的方法汇总: 1、门延时数量级的延时(几个ns),可用逻辑门来完成,但告诉综合器不要将其优化掉(不精确,误差大,常常不被推荐)。比如用两个非门(用constraint 来告诉synthesizer 不要综合掉这些逻辑)。 2、使用delay cell,lcell。 3、采用更快的时钟,通过计数器来实现,对于比较小的延时,用两个DFF 级联就 ..

[查看全文]

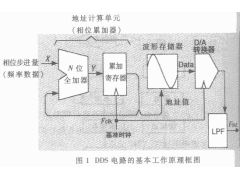

FPGA直接数字频率合成器的设计

2012-06-02

周俊峰 陈 涛

5

摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。 关键词:直接数字频率合成(DDS) 现场可编程门阵列(FPGA) 直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率 ..

[查看全文]

FPGA三国志-第二篇/结构篇

2012-06-02

wisdomz

8

Altera FPGA的速度没有Xilinx的速度快,错!当然这种非对称的结构,你必须有一定的了解,才可以更好的利用.也就是要遵循: 大的数据吞吐通道应该采用横向放置规划! 控制通路采用纵向放置规划! Altera至此以后,一直沿袭这种结构规划.因此,如果你想有效利用好Altera的产品,就应该遵守这个规则.但是要说明的,真正能体现性能的东西,也许 ..

[查看全文]

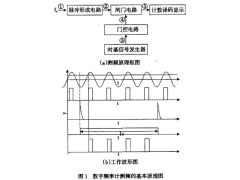

基于FPGA自适应数字频率计的设计

2012-06-02

陈尚志 胡荣强 胡合松

11

摘要:介绍一种以FPGA(Field Programmable Gate Array)为核心,基于硬件描述语言VHDL的数字频率计设计与实现。在介绍频率测量的原理和测量方法的基础上,针对所设计的频率计需简单易用的要求,采用FPGA和简单的外围电路使系统具有体积小、可靠性高、灵活性强及价格低廉等特点,同时还具有易于升级的特点。 在电子工程, ..

[查看全文]

Xilinx FPGA开发环境的配置

2012-06-02

风子心

20

一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录; C、运行compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。 注意:需要根据你安装的modelsim目录 ..

[查看全文]

推荐文章

最新文章

热门文章