异步FIFO的VHDL设计

2013-04-06

9

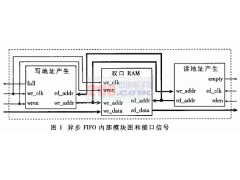

FIFO(先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口信号包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wren)和写数据(wr_data)、与读时钟同步的读有 ..

[查看全文]

VHDL 计数器源程序

2013-04-05

8

十五计数器library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; ENTITY fiveteencout IS PORT(clk,reset,enable : IN std_logic; count : OUT std_logic_vector(3 downto 0)); END fiveteencout; ARCHITECTURE counter OF fiveteencout IS SIGNAL count_int:std_logic_vector(0 to 3); BEGIN PROC ..

[查看全文]

4位乘法器vhdl程序

2013-04-01

11

4位乘法器,vhdl -- --------------------------------------------------------------------------------/ -- DESCRIPTION : Signed mulitplier: -- A (A) input width : 4 -- B (B) input width : 4 -- Q (data_out) output width : 7 -- Download from : http://www.pld.com.cn --------------------------------- ..

[查看全文]

Verilog讨论组精彩内容摘录

2013-03-31

12

问题:我遇到了一个问题,希望能得到帮助。 我在用FPGA(ALTERA 10K30)做仿真实验时,内部的计数器总是计数不正常,但是我在微机中用ModelSim仿真的结果是正确的,所以逻辑应该没有问题,问题出在FPGA,请教各位,我该如何解决这个问题。谢谢! I met a question,hope someone could do me a favor. when I used FPGA ..

[查看全文]

Verilog HDL设计练习进阶(八)

2013-03-28

7

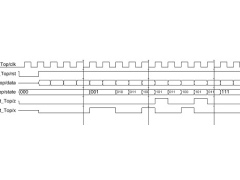

练习八. 利用有限状态机进行复杂时序逻辑的设计 目的:掌握利用有限状态机实现复杂时序逻辑的方法; 在数字电路中我们已经学习过通过建立有限状态机来进行数字逻辑的设计,而在Verilog HDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,我们可以直观地设计出适合更为复杂的时序逻辑的电路。关于 ..

[查看全文]

全数字锁相环的verilog源代码

2013-03-28

14

仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn); parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg ..

[查看全文]

VHDL设计举例:伪随机数产生器

2013-03-26

175

----------------------------------------------------------------------------- -- --The following information has been generated by Exemplar Logic and --may be freely distributed and modified. -- --Design name : pseudorandom -- --Purpose : This design is a pseudorandom number generator. This des ..

[查看全文]

VHDL中Loop动态条件的可综合转化

2013-03-25

24

引言 VHDL是一种硬件描述语言,于1983年被IEEE制定为国际标准IEEE1076。近年来国内引进和出版了不少教材,使其在国内得到迅速推广。由于VHDL最初目的是为了实现硬件的建模而被提出的,所以其措施能力超越了数字逻辑集成电路的范围。而现有的EDA工具基本上只能支持VHDL的子集,特别是针对FPGA/CPLD器件进行的不同的综 ..

[查看全文]

Verilog学习笔记

2013-03-16

8

一般认为 Verilog HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL要强的多 写了第一个verilog程序,是一个加法器内容如下 module adder(count,sum,a,b,cin); input[2:0] a,b; input cin; output count; output [2:0] sum; assign{count,sum}=a+b+cin; endmodule 开始编译出现了几次错误,后来发现给实体 ..

[查看全文]

Verilog模拟PS2协议

2013-03-14

12

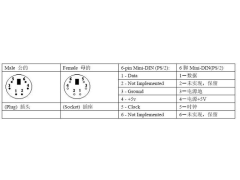

本来以为模拟PS2协议相当的麻烦,今天下了一本PS2协议手册看了半天,原来读键盘值相当简单嘛,比模拟SPI、I2C简单多了呵呵。 下面介绍一下具体过程 1.明确接线关系,只需接4根线,VCC要+5V,3.3我测试过不能用,时钟和数据线要用bidir双向口线,FPGA可以不用外接上拉电阻。另外,USB键盘也可以用,只要用一个转接头转成 ..

[查看全文]

从1394 VHDL代码移植看FPGA设计

2013-03-12

汪国有 龙翔林

13

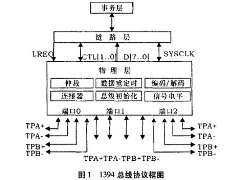

1 引言 IEEE1394是在计算机与外设直接进行高速数据传输的串行总线,因其具有传输速度高、支持即插即用、支持多达63个设备级联、以及设备间传输无需主机干预等特点,以至从其一出现就备受青睐。因IEEE 1394协议中的物理层可以在链路层不激活的情况下,作为中间节点而存在于1394网络中,物理层具有单独存在的意义,因此应用 ..

[查看全文]

一个好用的Verilog串口UART程序

2013-03-12

16

出自http://www.asic-world.com/,测试过了很好用。==========================================================================//----------------------------------------------------- // Design Name : uart // File Name: uart.v // Function: Simple UART // Coder: Deepak Kumar Tala //------- ..

[查看全文]

推荐文章

最新文章

热门文章